💡 Resumen (TL;DR):

- ASML diseña un sistema de unión híbrida junto a Prodrive Technologies y VDL-ETG para el empaque de semiconductores.

- El hardware aprovechará la tecnología MagLEV para alcanzar precisiones similares a las de sus actuales sistemas de 0.7 nanómetros.

- La empresa competirá con firmas como BESI en el ensamble de procesadores para IA y arquitecturas 3D multicapa.

ASML, la compañía neerlandesa que mantiene el monopolio de las máquinas de litografía ultravioleta extrema, está desarrollando equipos de unión híbrida para el empaque avanzado de semiconductores. El movimiento marca su expansión más agresiva hacia el mercado de hardware back-end, poniéndola a competir contra líderes del sector como ASMPT y BE Semiconductor Industries (BESI).

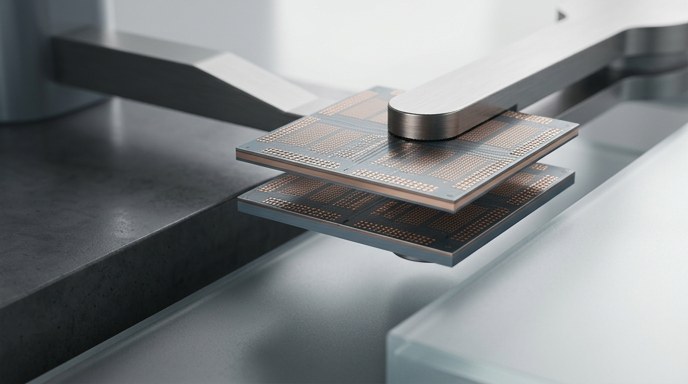

Unión híbrida es una técnica de ensamblaje que conecta directamente las superficies de cobre de dos chips sin usar los tradicionales bultos de metal. Esta tecnología permite interconexiones extremadamente densas, un requisito absoluto para crear las memorias de alto ancho de banda y los procesadores de inteligencia artificial actuales.

ASML construye la arquitectura del nuevo equipo junto con Prodrive Technologies y VDL-ETG, dos de sus socios históricos. Utilizarán tecnología de levitación magnética (MagLEV) que elimina la vibración asociada a los rodamientos de aire convencionales, logrando la alineación nanométrica que exige el apilamiento de chips.

Un experto de la industria declaró a TheElec que “el equipo de unión híbrida de ASML reconfigurará de inmediato el panorama actual del mercado”, citando como base la maquinaria High-NA EUV de la empresa, capaz de lograr una precisión de superposición de aproximadamente 0.7 nanómetros.

El futuro de las arquitecturas multicapa

La decisión de ASML responde a un auge financiero masivo en el sector de empaquetado. BESI reportó recientemente que su cartera de pedidos de cuarto trimestre se disparó un 105% frente al año anterior. A la par, el fabricante de litografía prepara el envío para el Q3 de 2025 de su TWINSCAN XT:260, un escáner DUV que, según el CEO Christophe Fouquet, cuadruplica la productividad de las soluciones existentes.

Marco Pieters, CTO de ASML, explicó a Reuters que se encuentra “revisando personalmente la composición del portafolio de productos” enfocados en el empaquetado. Tras evaluar las rutas de trabajo de compañías como SK Hynix, Pieters determinó que “la demanda por equipo de procesos de apilamiento es segura”.

- NVIDIA y AMD abandonaron las matrices monolíticas en favor de complejas arquitecturas de múltiples chips.

- Intel y TSMC impulsan el apilamiento 3D que requiere tolerancias métricas minúsculas.

- Las instalaciones de back-end ahora exigen la misma precisión de cuarto limpio que el procesamiento de obleas de silicio.

“La precisión se está volviendo cada vez más importante”, apuntó Pieters en su entrevista con Reuters. “Estamos considerando no solo los próximos cinco años, sino también los próximos diez, quizás quince años”.